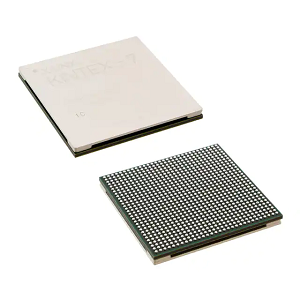

XC7K420T-2FFG901I – Integrované obvody, vstavané, programovateľné hradlové polia

Vlastnosti produktu

| TYP | ILUSTROVAŤ |

| kategórii | Integrované obvody (IC)Vložené Field Programmable Gate Arrays (FPGA) |

| výrobca | AMD |

| séria | Kintex®-7 |

| obal | podnos |

| Stav produktu | Aktívne |

| DigiKey je programovateľný | Neoverené |

| Číslo LAB/CLB | 32575 |

| Počet logických prvkov/jednotiek | 416960 |

| Celkový počet bitov RAM | 30781440 |

| Počet I/O | 380 |

| Napätie - Napájanie | 0,97V ~ 1,03V |

| Typ inštalácie | Typ povrchového lepidla |

| Prevádzková teplota | -40 °C ~ 100 °C (TJ) |

| Balík/Bývanie | 900-BBGA, FCBGA |

| Zapuzdrenie komponentov dodávateľa | 901-FCBGA (31x31) |

| Hlavné číslo produktu | XC7K420 |

| TYP | ILUSTROVAŤ |

| kategórii | Integrované obvody (IC)Vložené |

| výrobca | AMD |

| séria | Kintex®-7 |

| obal | podnos |

| Stav produktu | Aktívne |

| DigiKey je programovateľný | Neoverené |

| Číslo LAB/CLB | 32575 |

| Počet logických prvkov/jednotiek | 416960 |

| Celkový počet bitov RAM | 30781440 |

| Počet I/O | 380 |

| Napätie - Napájanie | 0,97V ~ 1,03V |

| Typ inštalácie | Typ povrchového lepidla |

| Prevádzková teplota | -40 °C ~ 100 °C (TJ) |

| Balík/Bývanie | 900-BBGA, FCBGA |

| Zapuzdrenie komponentov dodávateľa | 901-FCBGA (31x31) |

| Hlavné číslo produktu | XC7K420 |

FPGA

Výhody

Výhody FPGA sú nasledovné:

(1) FPGA pozostávajú z hardvérových zdrojov, ako sú logické bunky, RAM, násobiče atď. Racionálnym usporiadaním týchto hardvérových zdrojov možno implementovať hardvérové obvody, ako sú násobiče, registre, generátory adries atď.

(2) FPGA môžu byť navrhnuté pomocou blokových schém alebo Verilog HDL, od jednoduchých hradlových obvodov po obvody FIR alebo FFT.

(3) FPGA je možné donekonečna preprogramovať a načítať nové konštrukčné riešenie len za niekoľko stoviek milisekúnd, pomocou rekonfigurácie na zníženie réžie hardvéru.

(4) Pracovná frekvencia FPGA je určená čipom FPGA, ako aj konštrukciou a môže byť upravená alebo nahradená rýchlejším čipom, aby spĺňala určité náročné požiadavky (aj keď, samozrejme, prevádzková frekvencia nie je neobmedzená a môže zvýšiť, ale riadi sa súčasnými procesmi IC a inými faktormi).

Nevýhody

Nevýhody FPGA sú nasledovné:

(1) FPGA sa spoliehajú na hardvérovú implementáciu pre všetky funkcie a nemôžu implementovať operácie, ako napríklad vetvenie podmienených skokov.

(2) FPGA môžu implementovať iba operácie s pevným bodom.

Stručne povedané: FPGA sa spoliehajú na hardvér na implementáciu všetkých funkcií a možno ich porovnať s vyhradenými čipmi, pokiaľ ide o rýchlosť, ale existuje veľká medzera v flexibilite dizajnu v porovnaní s procesormi na všeobecné použitie.

Dizajnové jazyky a platformy

Programovateľné logické zariadenia sú hardvérové nosiče, ktoré konkretizujú zavedené funkcie a technické špecifikácie elektronických aplikácií prostredníctvom technológie EDA.FPGA, ako jedno z hlavných zariadení, ktoré implementujú túto cestu, sú priamo užívateľsky orientované, mimoriadne flexibilné a všestranné, ľahko použiteľné a rýchlo sa testujú a implementujú do hardvéru.

Hardware Description Language (HDL) je jazyk používaný na navrhovanie digitálnych logických systémov a popis digitálnych obvodov, pričom hlavné bežne používané sú VHDL, Verilog HDL, System Verilog a System C.

Jazyk popisu hardvéru veľmi vysokorýchlostných integrovaných obvodov (VHDL) ako všestranný jazyk na popis hardvéru sa vyznačuje tým, že je nezávislý od konkrétneho hardvérového okruhu a nezávislý od konštrukčnej platformy, s výhodami možnosti širokého popisu, nie v závislosti od konkrétnych zariadení a schopnosť opísať návrh komplexnej riadiacej logiky v rigoróznom a stručnom kóde atď. Je podporovaný mnohými spoločnosťami EDA a je široko používaný v oblasti elektronického dizajnu.široko používaný.

VHDL je vysokoúrovňový jazyk pre návrh obvodov a v porovnaní s inými jazykmi na popis hardvéru má vlastnosti jednoduchého jazyka, flexibility a nezávislosti od návrhu zariadenia, čo z neho robí bežný jazyk na popis hardvéru pre technológiu EDA a robí technológiu EDA viac. prístupné pre dizajnérov.

Verilog HDL je široko používaný jazyk na popis hardvéru, ktorý možno použiť vo viacerých fázach procesu návrhu hardvéru, vrátane modelovania, syntézy a simulácie.

Výhody Verilog HDL: podobne ako C, ľahko sa učí a je flexibilný.Rozlišujú sa malé a veľké písmená.Výhody pri písaní podnetov a modelovania.Nevýhody: veľa chýb sa nedá zistiť v čase kompilácie.

Výhody VHDL: Prísna syntax, jasná hierarchia.Nevýhody: dlhá doba oboznámenia sa, nedostatočná flexibilita.

Softvér Quartus_II je kompletné multiplatformové návrhové prostredie vyvinuté spoločnosťou Altera, ktoré dokáže splniť konštrukčné potreby rôznych FPGA a CPLD a je komplexným prostredím pre návrh programovateľných systémov na čipe.

Vivado Design Suite, integrované dizajnové prostredie vydané dodávateľom FPGA Xilinx v roku 2012. Zahŕňa vysoko integrované dizajnové prostredie a novú generáciu nástrojov od systémovej až po IC úroveň, všetko postavené na zdieľanom škálovateľnom dátovom modeli a spoločnom ladiacom prostredí.Xilinx Vivado Design Suite poskytuje jadrá FIFO IP, ktoré možno ľahko aplikovať na návrhy.